# Discrete Relay Output Signal Conditioning Card

# User Manual CQ9519-DO-16

| Concurrent Real-Time                                 | Document Number | 0810008         |  |

|------------------------------------------------------|-----------------|-----------------|--|

| 800 Northwest 33rd Street<br>Pompano Beach, FL 33064 | Revision        | A               |  |

|                                                      | Date            | August 04, 2025 |  |

|                                                      | Author          | JCMII           |  |

**Revision History**

| Revision | Date       | Author       | Changes            |

|----------|------------|--------------|--------------------|

| A        | 08/04/2025 | Jim Millener | UM Initial Release |

|          |            |              |                    |

|          |            |              |                    |

|          |            |              |                    |

|          |            |              |                    |

|          |            |              |                    |

|          |            |              |                    |

|          |            |              |                    |

|          |            |              |                    |

|          |            |              |                    |

#### TABLE OF CONTENTS

| . INTRODUCTION                       | 4  |

|--------------------------------------|----|

| 2. PRODUCT DESCRIPTION               | 4  |

| 2.1 Overview                         |    |

| B. BLOCK DIAGRAM                     |    |

| l. PICTURE                           |    |

| 5. GENERAL OPERATION                 | 7  |

| 5.1 Initial Configuration Setup      | 7  |

| 5.2 Feature Selections               |    |

| 5.3 Typical input circuit schematic  |    |

| 5.4 Typical output circuit schematic | 8  |

| 5. CIRCUIT ASSEMBLY                  | 9  |

| 7. TIMING                            | 9  |

| B. PHYSICAL CHARACTERISTICS          | 9  |

| O. EXTERNAL CONNECTORS               | 10 |

| 9.1 Digital Ouput Connector          | 10 |

| 9.2 Discrete Input Connector         |    |

| 9.3 Power Connector                  | 13 |

Signal Conditioning

#### 1. Introduction

This document describes the design and operational aspects of the Concurrent Real-Time CQ9519-DO-16 Configurable Discrete Relay Output Signal Conditioning Board.

## 2. Product Description

#### 2.1 Overview

The Discrete Relay Output Signal Conditioner is a board with 16 digital circuits that are designed to be a front end to Concurrent Real-Time digital output device, such as a WC-CP-FPGA-2, WC-CP-FPGA-3, WC-CP-FPGA-4, or WC-CP-FPGA-5 Programmable FPGA Cards, or other discrete digital output interfaces. There are two variants of the card, The standard version is designed to be installed into a CCRT Signal Workbench General Purpose Signal Conditioning (GPSD) chassis HS000-SIGWB-8. The DIN variant is designed to be mounted on a DIN rail. The board requires a power supply of +5VDC at 3W. The 16 outputs are galvanically isolated from each other. Each output provides a solid-state relay contact between plus and minus when activated. The output max voltage is 60V DC or AC peak. The peak current through the relay contacts is 4A. The on resistance of each relay is  $30m\Omega$ . The drive for the relays is jumper selectable between LVDS or 3.3V logic signals. These input drive signals can be provided by one of the CCRT cards mentioned before or by user input. The DIN Mount variant of the card requires an external power supply, such as the CCRT CX-NPSC-PWR1.

©2025 Concurrent Real-Time, Inc. Concurrent Real-Time product names are trademarks or registered trademarks of Concurrent Real-Time Inc. All other product names, logos, brands, trademarks and registered trademarks are property of their respective owners. Information subject to change without notice.

UNRESTRICTED

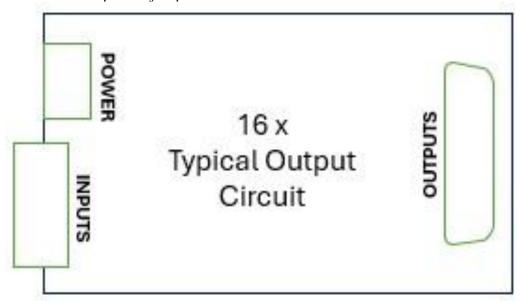

# 3. Block Diagram

Figure 1 shows a block diagram of the board identifying the I/O connectors. Figure 2 is a block diagram of the board showing the locations of the individual channel circuits that can be used to locate channel specific jumpers.

Figure 1

Figure 2

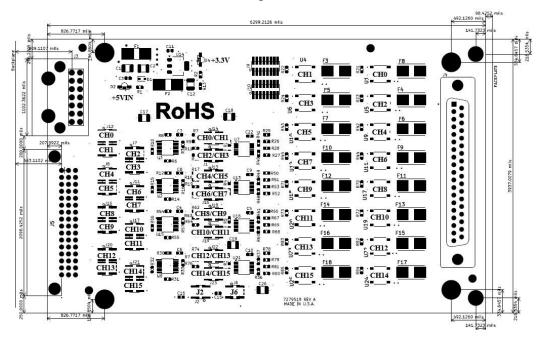

# 4. Picture

**Picture 1** is a picture of the Workbench mount board assembly.

Picture 1

# 5. General Operation

The following sections show the general steps required for operation.

#### 5.1 Initial Configuration Setup

- 1) Before powering on a system with this board in it, configure the jumpers as described in this document to make sure that the I/O is configured as necessary.

- 2) Connect cables from the I/O interface to the system.

- 3) After power is applied to the system, if the LEDs are visible, confirm that the +5V and the +3.3V indicators LED are ON.

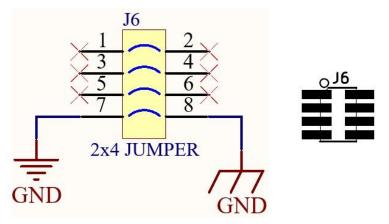

#### **5.2 Feature Selections**

There is one feature that is required to be set up to use the circuitry on this board and one feature that is optional. The mandatory set up feature is the enable or disable of the LVDS drivers. Header J2 which can be located using Figure 2 needs to be set for the LVDS drivers. This jumper is shown in Figure 4. Jumper pins 3-4 to enable the LVDS drivers and jumper pins 1-2 to disable the LVDS drivers. The optional feature is the ability to connect the circuit ground to the mechanical grounds of the board and the shield of the connectors. Figure 3 shows a schematic of the ground selection jumper.

Figure 3

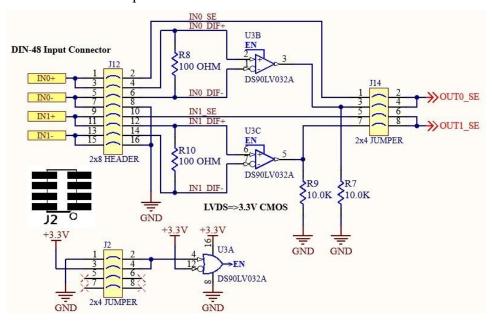

#### 5.3 Typical input circuit schematic.

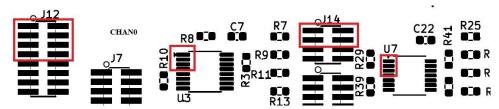

The typical input circuit is shown in Figure 4. The location of the jumper blocks is shown in Figure 2. For channels 0 and 1, jumper block J12 is used to connect the INx+ and INx- signals to the inputs of the LVDS drivers or bypass the LVDS drivers. If the LVDS is bypassed, the input levels should be +3.3V logic signals. The signals are then buffered and drive the digital isolators that provide the isolated outputs.

Figure 4

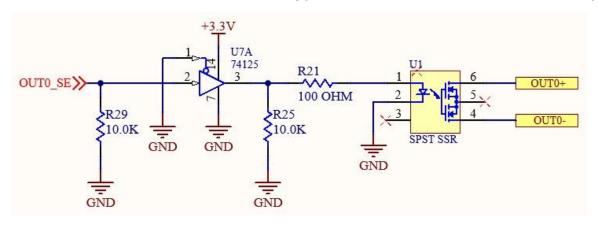

#### 5.4 Typical output circuit schematic.

Figure 5 shows the typical output circuit. The output presented to the user is a solid-state relay. The SSR contacts are rated at 4A with a  $30m\Omega$  on resistance and have a breakdown at 60V.

Figure 5

# 6. Circuit assembly

Figure 6 shows the layout of a single typical input circuit, channel 0 and the location of that typical's components.

Figure 6

# 7. Timing

The propagation delay through the circuit including the SSR is less than 1mS.

# 8. Physical Characteristics

The Discrete Relay Output Signal Conditioner Board is a 100mm X 160mm card that can be mounted on a DIN rail or in a 3U Signal Workbench chassis, HS000-SIGWB-8. Power consumption depends on the load, but the maximum total power consumption is less than 3 watts for the +5V supplies with all channels being used.

#### 9. External Connectors

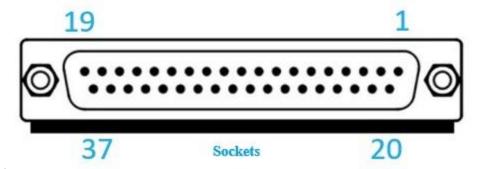

#### 9.1 Digital Output Connector

Outputs are connected to connector J4, a 37 Pin D-Sub connector. Inputs use a standard 3-row x 16-pin DIN style connector J5 which can be connected to a Signal Workbench backplane or cable depending on system requirements. The following shows the connector as viewed when looking at the board:

Figure 7

| DB37 Pin Assignment for CQ9519-DO-16 |       |                     |  |  |

|--------------------------------------|-------|---------------------|--|--|

| Pin Number                           | Name  | Description         |  |  |

| 1                                    | OUT0+ | High side output 0. |  |  |

| 20                                   | OUT0- | Low side output 0.  |  |  |

| 2                                    | OUT1+ | High side output 1. |  |  |

| 21                                   | OUT1- | Low side output 1.  |  |  |

| 3                                    | OUT2+ | High side output 2. |  |  |

| 22                                   | OUT2- | Low side output 2.  |  |  |

| 4                                    | OUT3+ | High side output 3. |  |  |

| 23                                   | OUT3- | Low side output 3.  |  |  |

| 5                                    | OUT4+ | High side output 4. |  |  |

| 24                                   | OUT4- | Low side output 4.  |  |  |

| 6                                    | OUT5+ | High side output 5. |  |  |

| 25                                   | OUT5- | Low side output 5.  |  |  |

| 7                                    | OUT6+ | High side output 6. |  |  |

| 26                                   | OUT6- | Low side output 6.  |  |  |

| 8                                    | OUT7+ | High side output 7. |  |  |

| 27                                   | OUT7- | Low side output 7.  |  |  |

Table 1

| DB37 Pin Assignment for CQ9519-DO-16 |        |                      |  |  |

|--------------------------------------|--------|----------------------|--|--|

| Pin Number                           | Name   | Description          |  |  |

| 9                                    | OUT8+  | High side output 8.  |  |  |

| 28                                   | OUT8-  | Low side output 8.   |  |  |

| 10                                   | OUT9+  | High side output 9.  |  |  |

| 29                                   | OUT9-  | Low side output 9.   |  |  |

| 11                                   | OUT10+ | High side output 10. |  |  |

| 30                                   | OUT10- | Low side output 10.  |  |  |

| 12                                   | OUT11+ | High side output 11. |  |  |

| 31                                   | OUT11- | Low side output 11.  |  |  |

| 13                                   | OUT12+ | High side output 12. |  |  |

| 32                                   | OUT12- | Low side output 12.  |  |  |

| 14                                   | OUT13+ | High side output 13. |  |  |

| 33                                   | OUT13- | Low side output 13.  |  |  |

| 15                                   | OUT14+ | High side output 14. |  |  |

| 34                                   | OUT14- | Low side output 14.  |  |  |

| 16                                   | OUT15+ | High side output 15. |  |  |

| 35                                   | OUT15- | Low side output 15.  |  |  |

| 17                                   | N/C    | No Connect           |  |  |

| 36                                   | GND    | Circuit GND          |  |  |

| 18                                   | GND    | Circuit GND          |  |  |

| 37                                   | GND    | Circuit GND          |  |  |

| 19                                   | GND    | Circuit GND          |  |  |

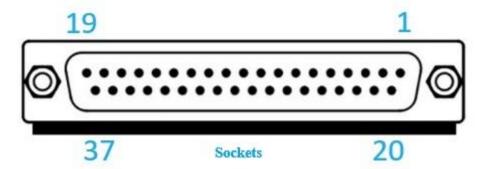

#### 9.2 Discrete Input Connector

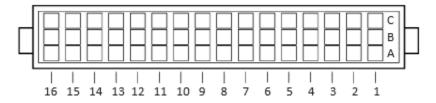

Figure 8 shows the discrete input connector and Table 2 shows the pin assignment, looking into the connector with the PCB below the connector body.

Figure 8

| DIN48 Pin Assignment for CQ9518-DI-16 |       |            |       |                   |            |      |             |

|---------------------------------------|-------|------------|-------|-------------------|------------|------|-------------|

| Pin<br>Num                            | Name  | Pin<br>Num | Name  | Description       | Pin<br>Num | Name | Description |

| A1                                    | IN15+ | B1         | IN15- | Discrete input 0  | C1         | N/C  | No connect  |

| A2                                    | IN14+ | B2         | IN14- | Discrete input 1  | C2         | N/C  | No connect  |

| А3                                    | IN13+ | В3         | IN13- | Discrete input 2  | C3         | GND  | Circuit GND |

| A4                                    | IN12+ | B4         | IN12- | Discrete input 3  | C4         | GND  | Circuit GND |

| A5                                    | IN11+ | B5         | IN11- | Discrete input 4  | C5         | GND  | Circuit GND |

| A6                                    | IN10+ | В6         | IN10- | Discrete input 5  | C6         | +5V  | +5V Supply  |

| A7                                    | IN9+  | В7         | IN9-  | Discrete input 6  | C7         | N/C  | No connect  |

| A8                                    | IN8+  | B8         | IN8-  | Discrete input 7  | C8         | N/C  | No connect  |

| A9                                    | IN7+  | В9         | IN7-  | Discrete input 8  | C9         | N/C  | No connect  |

| A10                                   | IN6+  | B10        | IN6-  | Discrete input 9  | C10        | N/C  | No connect  |

| A11                                   | IN5+  | B11        | IN5-  | Discrete input 10 | C11        | N/C  | No connect  |

| A12                                   | IN4+  | B12        | IN4-  | Discrete input 11 | C12        | N/C  | No connect  |

| A13                                   | IN3+  | B13        | IN3-  | Discrete input 12 | C13        | N/C  | No connect  |

| A14                                   | IN2+  | B14        | IN2-  | Discrete input 13 | C14        | N/C  | No connect  |

| A15                                   | IN1+  | B15        | IN1-  | Discrete input 14 | C15        | N/C  | No connect  |

| A16                                   | IN0+  | B16        | INO-  | Discrete input 15 | C16        | N/C  | No connect  |

Table 2

#### 9.3 Power Connector

Power connector pin assignment. Figure 9 is a view of the power connector looking into the pins on the PCB with the key on the top.

| 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|----|----|----|----|----|---|---|

| 7  | 6  | 5  | 4  | 3  | 2 | 1 |

Figure 9

**Table 3** shows the pin names and descriptions of the signals in the power connector.

|     | I .         | 1            |     |             |             |

|-----|-------------|--------------|-----|-------------|-------------|

| Pin | Signal Name | Description  | Pin | Signal Name | Description |

| 1   | No Connect  |              | 8   | No Connect  |             |

| 2   | No Connect  |              | 9   | No Connect  |             |

| 3   | No Connect  |              | 10  | No Connect  |             |

| 4   | No Connect  |              | 11  | No Connect  |             |

| 5   | GND         | Board Ground | 12  | No Connect  |             |

| 6   | GND         | Board Ground | 13  | No Connect  |             |

| 7   | GND         | Board Ground | 14  | P5V         | +5V Supply  |

Table 3